”数字逻辑 Verilog“ 的搜索结果

特点: 基于Basys3的实验教程, 共20个实验, 给出详细的实验步骤与源码.

数字逻辑课程的上机作业 用Verilog HDL 语言编写七段数码管的显示程序

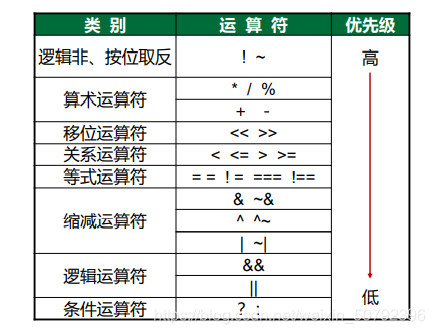

来源:网络素材Verilog语法的基本概念一、Verilog HDLVerilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一种行为描述的语言也是一种...

数字逻辑实验verilog代码

本系列文章基于罗杰老师的verilog HDL入门与FPGA系统设计介绍一些典型的模块verilog语言编写。

个单元的, 还有打印语句等, 也是门器件无法实现的。在设计的时候要确保所写的代码是可以综合的。具就会去元件库里调用一个二输入与门, 将输入端分别接上 b 和 c, 输出端接上 a。这种信号边沿触发, 即信号上升沿...

数字逻辑Verilog实验是指利用Verilog硬件描述语言来对数字逻辑电路进行实验的过程。Verilog是一种硬件描述语言,它可以用于对数字逻辑电路进行建模、仿真和验证。 在数字逻辑Verilog实验中,首先需要明确实验的目的...

数字逻辑Verilog运算课程设计是为了加深学生对于数字逻辑和Verilog编程的理解和应用能力,通过设计、编写和仿真数字逻辑电路和Verilog代码,让学生能够熟练掌握数字逻辑的基本概念和设计方法,并能运用Verilog语言...

通过本章的学习,读者将建立起坚实的数字逻辑电路理论基础,为后续的Verilog编程学习打下扎实的基础。 # 2. Verilog编程概述 Verilog编程是数字电路设计中常用的一种硬件描述语言,它可以描述电路的结构和行为,并...

主要是数字ic设计入门之verilog学习

华中科技大学 数电课程设计 数字逻辑 verilog自动销售机 vivado项目工程源码

OUC数字逻辑Verilog实验二 用Verilog实现4位计数器(时序逻辑)

Verilog是一种硬件描述语言(HDL),在数字逻辑设计中被广泛应用。它是一种基于事件驱动的并发编程语言,可以用于描述数字系统的行为和结构。Verilog语言的作用主要有两个方面: - 设计:Veril

数字钟从原理上讲是一种典型的数字电路,包括了组合逻辑电路和时序逻辑电路。这次设计就 是基于 EDA/SOPC 系统开发平台和八位数码管显示模块,运用 Quartus Ⅱ开发软件,设计一个多功能数字钟。

大学,数字逻辑基础与verilog硬件描述语言课后答案。通过verilog语言

包含全部西工大计算机学院数字逻辑与verilog设计实验三课堂检测代码以及实验内容,不含报告!

- **数据流建模**。输入信号经过**组合逻辑电路**传到输出时类似于数据流动,而不会在其中存储...结构描述方式就是将硬件电路描述成一个**分级子模块系统**,通过逐层调用这些子模块构成功能复杂的数字逻辑电路和系统。

资源包括:1.第二次实验内容 2.第二次实验所有代码以及modelsim项目 3.完整的第二次实验报告

0-7 8-F 双排按键输入器件驱动 防抖动、防多次采样

资源包括:1.第三次实验完整实验报告(两份)2.第三次实验所有代码及modelsim项目 3.第三次实验内容

资源包括:1.modelsim10.2(bug少版本)安装包 2.完整实验报告一 3.第一次实验内容 4.第一次实验所需代码,包括modelsim项目

《数字逻辑基础与Verilog设计》(原书第2版)系统介绍数字逻辑基本概念与实际应用。主要内容包括:逻辑电路、组合逻辑、算术运算电路、存储元件、同步时序电路(有限状态机)、异步时序电路、测试等。《数字逻辑基础与...

包含全部西工大计算机学院数字逻辑与verilog设计实验四课堂检测代码以及实验内容,不含报告!

**数字逻辑基础与verilog设计实验过程* 第二次实验过程记录: 1.将Quartus 20.1与modelsim 10.1安装完成后打开Quartus 20.1,并编译如下电路程序 2.新建文件并将其保存在相应位置后选择下一步,新建名暂时略过,...

从算法设计到硬线逻辑的实现--复杂数字逻辑系统的 Verilog HDL 设计技术和方法

用于学习fpga使用,是学习Veilog语言与硬件结合的基础。

推荐文章

- confluence搭建部署_ata confluence-程序员宅基地

- SpringCloud与SpringBoot版本对应关系_springboot 2.1.1 对于的cloud-程序员宅基地

- 如何恢复硬盘数据?简单解决问题_磁盘恢复 csdn-程序员宅基地

- 苹果手机测试网络速度的软件,App Store 上的“网速测试大师-测网速首选”-程序员宅基地

- 教了一年少儿编程,说说感想和体验-程序员宅基地

- 22东华大学计算机专硕854考研上岸实录-程序员宅基地

- 如何用《玉树芝兰》入门数据科学?-程序员宅基地

- macOS使用brew包管理器_brew清理缓存-程序员宅基地

- 【echarts没有刷新】用按钮切换echarts图表的时候,该消失的图表还在,加个key属性就解决了_echarts 怎么加key值-程序员宅基地

- 常用机器学习的模型和算法_常见机器学习模型算法整理和对应超参数表格整理-程序员宅基地